[메모리 가상화 #4] 페이징 본문

개요

운영체제는 거의 모든 공간 관리 문제를 해결할 때 두 가지 중 하나를 사용한다.

- 우리가 가상 메모리의 세그멘테이션에서 보았듯이 가변 크기 조각을 분할하는 것이다.

- 이 해결책은 태생적인 문제를 가지고 있다. 공간을 다양한 크기의 청크로 분할할 때 공간 자체가 단편화(fragmented) 될 수 있고, 할당은 점점 더 어려워진다.

- 두 번째 방법인 공간을 동일한 크기의 조각으로 분할하는 것을 고려해볼 필요가 있다.이를 페이징(Paging)이라 부른다.이 각각의 고정 크기 단위를 페이지(Page) 라고 부르고, 물리 메모리도 페이지 프레임이라고 불리는 고정 크기의 슬롯의 배열이라고 생각한다. 이 프레임 각각은 하나의 가상 메모리 페이지를 저장할 수 있다.

- 프로세스의 주소 공간을 몇개의 가변 크기의 논리 세그멘트(코드, 힙, 스택) 으로 나누는 것이 아니라 고정 크기의 단위로 나눈다.

핵심 질문

- 페이지를 사용하여 어덯게 메모리를 가상화 할 수 있을까?

- 세그멘테이션의 문제점을 해결하기 위해 페이지를 사용하여 어떻게 메모리를 가상화할 수 있는가

- 기본적인 기법은 무엇인가?

- 공간과 시간 오버헤드를 최소로하면서 그 기법을 잘 동작하게 만들기 위한 방법은 무엇인가?

간단한 예제

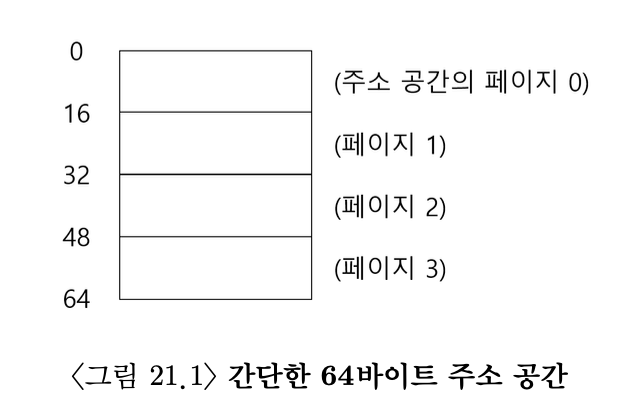

- 위 그림은 총 크기가 64바이트이면서 4개의 16바이트 페이지로 구성된 작은 주소 공간의 예를 보여준다.

- 실제 주소 공간은 훨씬 커서 32비트의 경우 4GB, 64비트의 경우에는 그보다 훨씬 크다.

- 물리메모리는 21.2 그림 처럼 고정 크기의 슬롯들로 구성된다.

- 이 경우에는 8개의 페이지 프레임, 총 128바이트의 비현실적으로 작은 물리 메모리이다.

- 가상 주소 공간의 페이지들은 물리 메모리 전체에 분산 배치되어 있다.

- 또한 운영체제가 자기자신을 위해서 물리메모리의 일부를 사용하고 있다.

- 페이징은 이전 방식(세그멘테이션)보다 더 많은 장점을 가지고있다.

- 유연성

- 페이징을 사용하면 프로세스의 주소 공간 사용방식과는 상관없이 효율적으로 주소 공간 개념을 지원할 수 있다.

- 예를들어 힙과 스택이 어느방향으로 커지는가, 어떻게 사용되는가에 대한 가정을 하지 않아도 된다.

- 빈 공간 관리의 단순함

- 우리의 작은 64 바이트 주소 공간(4페이지짜리) 을 8페이지크기의 물리 메모리에 배치하기를 원한다고 할 때, 운영체제는 비어있는 네 개의 페이지만 찾으면 된다.

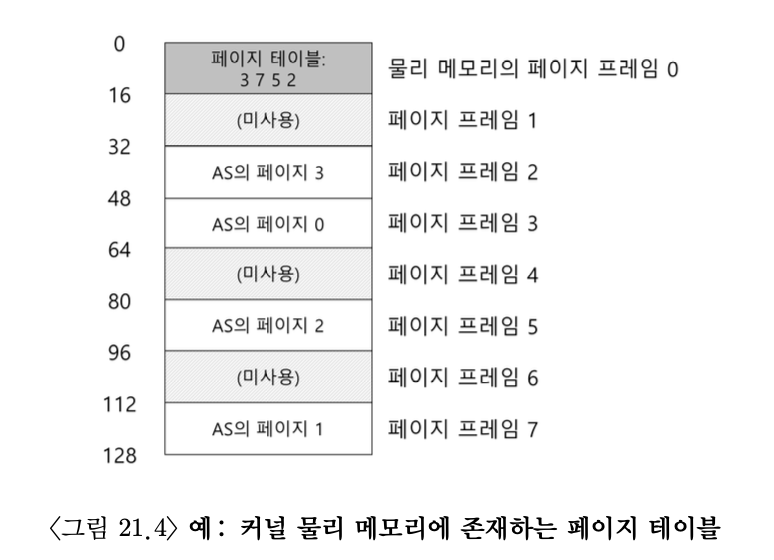

- 위 예제에서는 가상페이지 0을 물리 프레임 3에, 가상 페이지1을 물리 프레임 7 페이지 2를 프레임 5 그리고 페이지 3을 프레임 2에 배치하였다.

- 유연성

페이지 테이블

주소 공간의 각 가상 페이지에 대한 물리 메모리 위치 기록을 위하여 운영체제는 프로세스 마다 페이지 테이블이라는 자료 구조를 유지한다.

- 페이지 테이블의 주요 역할은 주소 공간의 가상 페이지 주소 변환 정보를 저장하는 것이다.

- 각 페이지가 저장된 물리 메모리의 위치가 어디인지 알려준다.

- 이전 예제의 경우 페이지 테이블은 다음과 같은 4개의 항목을 가진다.

- (가상 페이지 0 → 물리 프레임 3), (VP 1→ PF 7), (VP 2→ PF 5) 및 (VP 3 → PF 2)

- 페이지 테이블 프로세스마다 존재한다는 사실을 숙지해야 한다. (우리가 논의하는 대부분의 페이지 테이블 구조는 프로세스 마다 존재하는 구조이다. 역 페이지 테이 블(inverted page table)이라는 예외적인 기법도 있다)

- 예) 작은 주소 공간(64바이트)을 가진 프로세스가 다음 메모리 접근을 수행한다고 가정하자.

movl <virtual address>, %eax

- virtual address의 데이터를 eax 레지스터에 탑재한다.

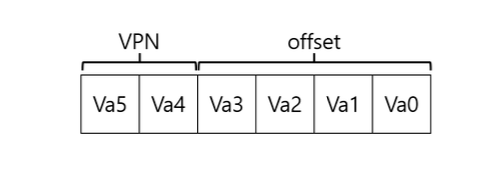

- 프로세스가 생성한 가상 주소의 변환을 위해 먼저 가상 주소를 가상 페이지 번호(virtual page number, VPN)와 페이지 내의 오프셋 2개의 구성 요소로 분할한다.

- 이 예에서는 가상 주소 공간의 크기가 64바이트이기 때문에 가상 주소는 6비트가 필요하다.

- 이 그림에서 Va5는 가상 주소의 최상위 비트, Va0는 최하위 비트

- 우리는 페이지 크기(16바이트)를 알고 있기 때문에, 다음과 같이 가상주소를 나눌 수 있다.

- 페이지 크기는 64바이트의 주소 공간에서 16바이트이다. 따라서 4페이지를 선택할 수 있어야하고, 최소의 최상위 2개의 비트(VPN)이 그 역할을 한다.

- 나머지 비트는 페이지 내에서 우리가 원하는 바이트의 위치를 나타낸다. 이것을 오프셋이라 부른다.

- Offset 비트 수 = 페이지 크기(log₂(PageSize))

- VPN 비트 수 = 전체 가상주소 비트 수 – Offset 비트 수

- 예를들어 위 탑재 명령어의 가상 주소가 21이라고 하자.

movl 21, %eax

- 21을 이진 형식으로 변환하면 010101을 얻고, 이 가상 주소를 검사하고 가상 페이지 번호와 오프셋으로 나눈다.

- 21은 VPN 1번, Offset 5이다. 이 가상 페이지 번호와 오프셋을 활용하여 어느 물리 프레임에 저장되어있는지 찾을 수 있다.

- 위의 페이지 테이블에서 물리 프레임 번호(physical frame number, PFN) 혹은 물리 페이지 번호(physical page number, PPN)는 7이다.

- 오프셋은 페이지 내에서 우리가 원하는 위치를 알려준다.

- 최종적으로 계산된 물리 주소는 1110101 이며 이곳이 탑재할 데이터가 저장된 정확한 위치이다.

페이지 테이블은 어디에 저장되는가

- 페이지 테이블은 작은 세그멘트 테이블이나 베이스-바운드 쌍에 비해매우 커질 수 있다.

- 물리 주소로의 변환 정보와 다른 필요한 정보를 저장하는 페이지 테이블 항목(page table entry, PTE)

- 32비트 주소 공간, 페이지 크기 4 KB인 경우

- 가상 주소: 20 비트 VPN + 12 비트 오프셋

- 필요 PTE 수: 2²⁰개(≈백만 개)

- PTE당 4 바이트 가정 시, 프로세스당 페이지 테이블 크기 ≈ 4 MB

- 실행 중인 프로세스가 100개라면 페이지 테이블만으로 약 400 MB의 메모리 소모

- 32비트 주소 공간, 페이지 크기 4 KB인 경우

- 페이지 테이블 전체를 MMU 회로에 상주시키기에는 크기가 너무 큼

- 메인 메모리(물리 메모리) 상의 커널 관리 영역에 저장

- 운영체제가 PTE 데이터 구조를 할당·관리

- 필요 시 운영체제 자신의 가상 메모리에 배치 가능

- 메모리 압박이 심해지면 디스크로 스왑(또는 페이징 아웃)

페이지 테이블에는 실제 무엇이 있는가

페이지 테이블의 역할

- 가상 페이지 번호(VPN)를 물리 프레임 번호(PFN)로 매핑하는데 사용되는 자료구조

- 변환 정보 외에 유효성·보호·이동 여부 등을 관리

선형 페이지 테이블(linear page table)

- 가장 간단한 배열 형태의 페이지 테이블

- 인덱스로 VPN을 사용해 곧바로 해당 PTE(page table entry)에 접근

기본 PTE 필드

| Valid bit | 해당 VPN→PFN 변환이 유효한지 표시 (할당되지 않은 페이지는 invalid) |

| Protection bit | 페이지가 읽을 수 있는지, 쓸 수 있는지, 또는 실행될 수 있는지를 표시 |

| Present bit | 페이지가 물리 메모리에 있는지 vs. 디스크(스왑 영역)에 있는지 표시 |

| Dirty bit | 메모리에 로드된 이후 페이지 내용이 변경되었는지 표시 |

| Reference bit(또는 accessed bit) | 페이지가 최근에 접근(access)되었는지 표시 (교체 알고리즘의 히트율 판단에 사용) |

x86 아키텍처의 PTE 비트 구성

| Present | P | 페이지가 메모리에 있으면 1, 스왑 아웃 시 0 |

| Read/Write | R/W | 0: 읽기만 허용, 1: 읽기·쓰기 모두 허용 |

| User/Supervisor | U/S | 0: 커널 모드만 접근, 1: 사용자 모드도 접근 허용 |

| PWT | Page Write-Through | 캐시 쓰기 정책 제어 (쓰기-스루 vs. 쓰기-백) |

| PCD | Page Cache Disable | 캐시 사용 여부 제어 |

| PAT | Page Attribute Table | 메모리 유형(attribute) 지정 (e.g. WC, WT, WB 등) |

| G | Global | 전역 페이지 표시: 프로세스 컨텍스트 전환 시에도 TLB에서 유지 |

| A | Accessed | 하드웨어가 페이지 접근 시 자동 설정 (교체 알고리즘에 사용) |

| D | Dirty | 하드웨어가 쓰기 시 자동 설정 (스왑 시 변경 여부 판단) |

| PFN | — | 물리 프레임 번호 (실제 물리 주소의 상위 비트) |

너무 느린 페이징

- 시스템은 프로세스의 페이지 테이블에서 적절한 페이지 테이블 항목을 가져와야 하고, 변환을 수행한 후, 물리 메모리에서 데이터를 탑재한다.

- 메모리 사용량 증가

- 각 프로세스마다 가상-물리 주소 변환 정보를 저장하는 페이지 테이블이 필요하므로, 프로세스 수가 많아질수록 페이지 테이블 크기가 크게 늘어남

- 추가 메모리 접근 비용

- 모든 메모리 참조(load/store 및 명령어 반입)에 대해 “변환 정보(PTE)”를 얻기 위해 한 번의 추가 메모리 접근이 필요합니다. 이로 인해 전체 처리 속도가 2배 이상 느려짐

- 모든 메모리 참조(load/store 및 명령어 반입)에 대해 “변환 정보(PTE)”를 얻기 위해 한 번의 추가 메모리 접근이 필요합니다. 이로 인해 전체 처리 속도가 2배 이상 느려짐

요약

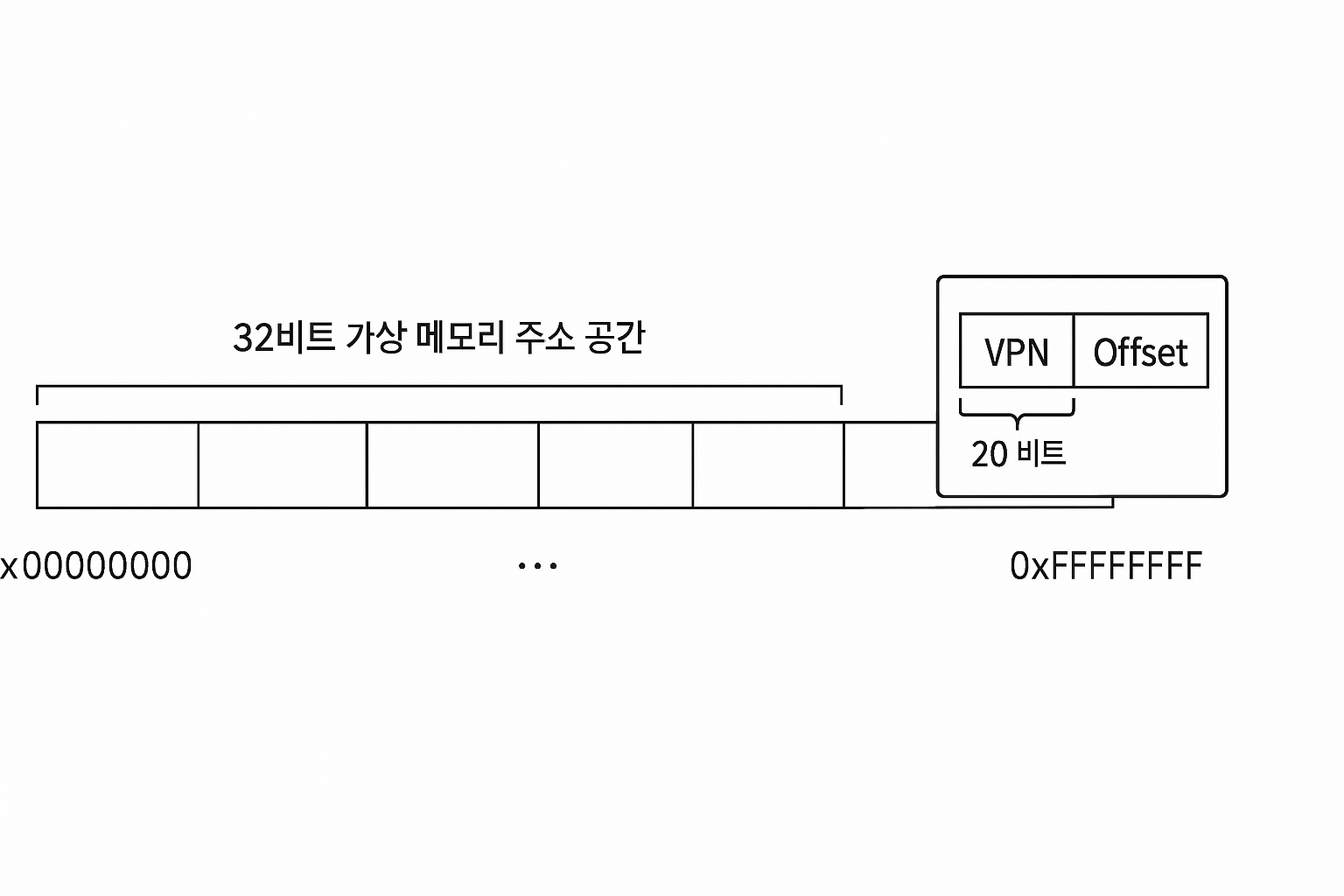

32비트 가상 주소 공간(0x00000000 ~ 0xFFFFFFFF)을 4KB(2¹²바이트) 단위로 나눈 모습

- 왼쪽 끝은 0x00000000, 오른쪽 끝은 0xFFFFFFFF로, 총 4GB(2³²바이트) 주소 범위

- 각 사각형은 4KB 페이지 하나를 의미하며, 전체적으로 1,048,576개의 페이지가 연속

이 구조를 통해, 메모리 관리 유닛(MMU)은 가상 주소의 VPN을 페이지 테이블로 매핑하여 물리 프레임 번호를 얻고, Offset을 더해 실제 물리 주소로 변환

- VPN (Virtual Page Number)

- 가상주소의 상위 비트로, “어느 페이지”인지 식별

- TLB나 페이지 테이블을 조회해 해당 가상페이지에 대응되는 물리프레임 번호(PFN)를 얻음

- Offset

- 가상주소의 하위 비트로, “그 페이지 안에서 어느 위치(바이트 오프셋)”인지 지정

- PFN에 이 Offset을 더해 최종 물리주소를 완성

VPN으로 페이지 단위 매핑을 처리하고, Offset으로 그 페이지 내부의 정확한 바이트 오프셋을 결정해서 최종적으로 정확한 물리 메모리 주소를 얻는 구조입니다.

출처 : 운영체제: 아주 쉬운 세 가지 이야기

'Fundamentals > OS' 카테고리의 다른 글

| [메모리 가상화 #6] 페이지 스왑, 페이지 폴트 (1) | 2025.07.02 |

|---|---|

| [메모리 가상화 #5] 페이징: TLB (1) | 2025.07.01 |

| [메모리 가상화 #3] 빈 공간 관리 (1) | 2025.06.28 |

| [메모리 가상화 #2] 세그멘테이션 (0) | 2025.06.28 |

| [메모리 가상화 #1] 멀티프로그래밍, 주소공간, 주소공간 변환 (2) | 2025.06.20 |

Comments